#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual is the best copy we could find; it may be incomplete or contain dated information. If we find a more recent copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available. You will find any other available product information on the Agilent Test & Measurement website, <a href="https://www.tm.agilent.com">www.tm.agilent.com</a>.

#### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. In other documentation, to reduce potential confusion, the only change to product numbers and names has been in the company name prefix: where a product number/name was HP XXXX the current name/number is now Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

#### **Your Comments Please**

#### **HP E2423A**

Your comments assist us in meeting your needs better. Please complete this questionnaire and return it to us. Feel free to add any additional comments that you might have. All comments and suggestions become the property of Hewlett-Packard. Omit any questions that you feel would be proprietary.

|                  |                         |                            |                              | Yes     | No |

|------------------|-------------------------|----------------------------|------------------------------|---------|----|

| l. Did you rec   | eive your product w     | hen expected?              |                              | []      | [] |

| 2. Were you sa   | atisfied with the ope   | ration of the preprocesso  | r interface at turn-on?      | []      | [] |

| •                | f not, what was missi   | •                          |                              |         |    |

|                  | Cable(s) [ ]            | Manual(s) [ ]              | Other                        |         |    |

| 4. What measu    | rements will this pro   | eprocessor interface be us | sed to make?:                |         |    |

|                  |                         | 0                          |                              | ·       |    |

| . which logic    | analyzer are you usi    | =                          |                              |         |    |

|                  | Туре                    |                            | <u></u>                      |         |    |

| 5. What do you   | u like most about the   | e preprocessor interface?: |                              |         |    |

|                  |                         |                            |                              |         |    |

| -                |                         |                            |                              |         |    |

|                  |                         |                            |                              |         |    |

| . What would     | d you like to see char  | nged or improved?          |                              |         |    |

|                  |                         |                            |                              |         |    |

| 3. Which section | ons of the manual ha    | ave you used?              |                              |         |    |

|                  | Installation Overv      | •                          |                              |         |    |

|                  | ] Step-By-Step Prod     | cedures                    |                              |         |    |

|                  | ] Specifications        |                            |                              |         |    |

| [                | ] Schematics and Pa     | arts List                  |                              |         |    |

| . Please rate t  | the manual on the fo    | ollowing:                  |                              |         |    |

|                  | 4= Excellent            | 3= Good                    | 2= Adequate                  | 1= Poor |    |

| 1                | ] Breadth and dept      | h of information           |                              |         |    |

|                  | ] Ability to easily fir |                            |                              |         |    |

| _                |                         |                            | ation provided in the manual |         |    |

|                  |                         |                            |                              |         |    |

| Please exp       | olain:                  |                            |                              |         |    |

| 1                | ·                       |                            |                              |         |    |

| 0 What is you    | ur experience with lo   | ogic analyzers and preprod | ressor interfaces?           |         |    |

| •                | No previous expen       |                            | essor interfaces.            |         |    |

| -                | Less than 1 year e      |                            |                              |         |    |

|                  |                         | s experience on one mode   | ıl                           |         |    |

|                  |                         | s experience on several m  |                              |         |    |

| N                | Jame                    |                            | Company                      |         |    |

|                  |                         |                            | Zip Code                     |         |    |

|                  | duress                  |                            | Zip Code                     |         |    |

THANK YOU FOR YOUR HELP

NO POSTAGE NECESSARY IF MAILED IN U.S.A.

#### Herstellerbescheinigung

Hiermit wird bescheinigt, daß das Gerät/System

#### HP 1650A/B and HP 1651A/B

in Übereinstimmung mit den Bestimmungen von Postverfügung 1046/84 funkentstört ist.

Der Deutschen Bundespost wurde das Inverkehrbringen dieses Gerätes/Systems angezeigt und die Berechtigung zur Überprüfung der Serie auf Einhaltung der Bestimmungen eingeräumt.

Zusatzinformation für Meß- und Testgeräte

Werden Meß- und Testgeräte mit ungeschirmten Kabeln und/oder in offenen Meßaufbauten verwendet, so ist vom Betreiber sicherzustellen, daß die Funk-Entstörbestimmungen unter Betriebsbedingungen an seiner Grundstücksgrenze eingehalten werden.

#### Manufacturer's declaration

This is to certify that this product HP 1650A/B and HP 1651A/B meets the radio frequency interference requirements of directive Vfg. 1046/84. The German Bundespost has been notified that this equipment was put into circulation and was granted the right to check the product type for compliance with these requirements.

Additional Information for Test- and Measurement Equipment

Note: If test and measurement equipment is operated with unshielded cables and/or used for measurements on open set-ups, the user must insure that under these operating conditions, the radio frequency interference limits are met at the border of his premises.

Note: This declaration indicates compliance of this product with the German RFI specifications stated in the German Vfg. 1046/84 directive.

# HP E2423A SCSI Bus Preprocessor Interface User's Guide

for the HP 1650A, HP 1650B, HP 1652B, HP 1660A/61A/62A/63A, HP 16510A, HP 16510B, HP 16511B, HP 16540/16541A,D, HP 16542A, and HP 16550A Logic Analyzers

Copyright Hewlett Packard Company 1992

Manual Part Number E2423-90904 Microfiche Part Number E2423-90804

Printed in U.S.A November 1992

#### **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition is published.

A software code may be printed before the date; this indicates the version of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

Edition 1 November 1992 E2423-90904

#### **List of Effective Pages**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. If an update is incorporated when a new edition of the manual is printed, the change dates are removed from the bottom of the pages and the new edition date is listed in the Printing History and on the title page.

Pages Effective Date

#### **Product Warranty**

This Hewlett-Packard product has a warranty against defects in material and workmanship for a period of 1 year from date of shipment. During warranty period, Hewlett-Packard Company will, at its option, either repair or replace products that prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Hewlett-Packard. However, warranty service for products installed by Hewlett-Packard and certain other products designated by Hewlett-Packard will be performed at Buyer's facility at no charge within the Hewlett-Packard service travel area. Outside Hewlett-Packard service travel areas, warranty service will be performed at Buyer's facility only upon Hewlett-Packard's prior agreement and Buyer shall pay Hewlett-Packard's round trip travel expenses.

For products returned to Hewlett-Packard for warranty service, the Buyer shall prepay shipping charges to Hewlett-Packard and Hewlett-Packard shall pay shipping charges to return the product to the Buyer. However, the Buyer shall pay all shipping charges, duties, and taxes for products returned to Hewlett-Packard from another country.

Hewlett-Packard warrants that its software and firmware designated by Hewlett-Packard for use with an instrument will execute its programming instructions when properly installed on that instrument. Hewlett-Packard does not warrant that the operation of the instrument, software, or firmware will be uninterrupted or error-free.

### Limitation of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HEWLETT-PACKARD SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **Exclusive** Remedies

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### **Assistance**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For assistance, contact your nearest Hewlett-Packard Sales and Service Office.

#### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### Safety

This product has been designed and tested according to International Safety Requirements. To ensure safe operation and to keep the product safe, the information, cautions, and warnings in this user's guide must be heeded.

### **Table of Contents**

|   | 4  |    |   |     | •   |   |

|---|----|----|---|-----|-----|---|

| ı | nt | ro | a | uct | ıoı | n |

Logic Analyzers Supported How to Use This Manual

| Chapter 1: | Setting Up the HP E2423A                            |      |

|------------|-----------------------------------------------------|------|

| Chapter 1. | <u> </u>                                            |      |

|            | Introduction                                        |      |

|            | Duplicating the Master Disk                         |      |

|            | HP 16500A Software Compatibility                    |      |

|            | Equipment Supplied                                  |      |

|            | Equipment Required                                  |      |

|            | Installation Quick Reference                        |      |

|            | Setting Up the HP E2423A Front Panel                |      |

|            | Connecting the HP E2423A to the SCSI Bus            |      |

|            | Connecting to the HP E2423A                         |      |

|            | Power Up / Down Sequence                            |      |

|            | Setting Up the Analyzer from the Disk               |      |

|            | Loading an Inverse Assembler                        |      |

|            | Selecting the Correct Inverse Assembler             | 1-12 |

| Chapter 2: | Analyzing the SCSI Bus                              |      |

|            | Introduction                                        | 2    |

|            |                                                     |      |

|            | Format Specification                                |      |

|            | Symbols and Labels                                  |      |

|            | Accumulating Data                                   |      |

|            | Listing Menu                                        |      |

|            | The SCSI Bus Inverse Assemblers                     |      |

|            | Interpreting Commands                               |      |

|            | Interpreting Vendor Unique and Reserved Information |      |

|            | Interpreting Messages                               |      |

|            | Interpreting Status                                 |      |

|            | Interpreting Data                                   |      |

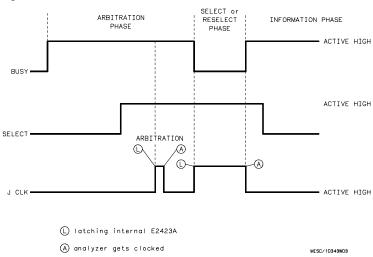

|            | Arbitration, Select, and Reselect Phases            |      |

|            | Attention, Reset and Bus Free                       |      |

|            | Parity Error                                        |      |

|            | The Trace Menu                                      |      |

|            | LED Indicators                                      | 2-13 |

Contents-1

| Chapter 3:  | Additional Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

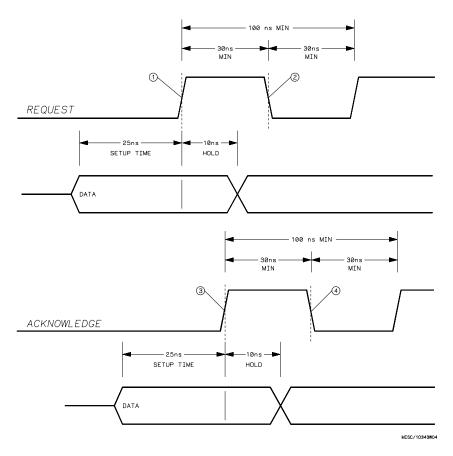

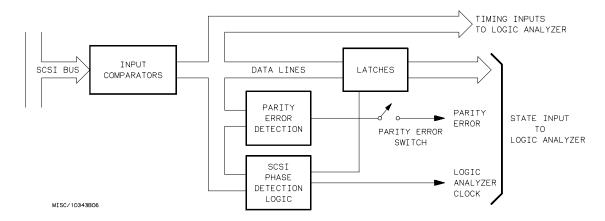

| •           | Introduction3-1Characteristics3-1Clocking3-3Interface Description3-6SCSI Bus Signal to HP E2423A Connector Mapping3-7Servicing3-11                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Appendix A: | SCSI Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Appendix B: | Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|             | "Slow or Missing Clock". B-1 No Activity on Activity Indicators B-1 Slow Clock. B-2 "No Configuration File Loaded". B-2 "Selected File is Incompatible". B-2 ". Inverse Assembler Not Found". B-3 No Inverse Assembly. B-3 Incorrect Inverse Assembly. B-3 "State Clock Violates Overdrive Specification". B-3 "Unwanted Triggers. B-3 "Waiting for Trigger". B-4 Intermittent Data Errors. B-4 Intermittent Data Errors. B-4 "Time from Arm Greater Than 41.93 ms.". B-4 No Setup/Hold Field on Format Screen. B-4 "Default Calibration Factors Loaded" (16540/41/42). B-4 |  |  |  |  |  |

Contents-2

#### Introduction

The HP E2423A Small Computer Systems Interface (SCSI) Bus Preprocessor Interface provides a complete mechanical and electrical connection between an 8-bit or 16-bit Single-Ended or Differential SCSI Bus system and a variety of HP logic analyzers. Switches on the front panel allow you to the select the appropriate bus type, bus size, and parity. LED lights as indicators allow you to look at the static condition of the bus at a quick glance. The HP E2423A software provides inverse assembly of activity on the buses, and configurations for the logic analyzers.

#### Logic Analyzers Supported

The following logic analyzers are supported by the HP E2423A Preprocessor Interface:

#### HP 1650A (requires memory upgrade)

This logic analyzer provides 1 k of memory depth with either 80 channels of 25 MHz state analysis or 80 channels of 100 MHz timing analysis.

Due to the memory requirements for the HP E2423A inverse assemblers, the HP 1650A Logic Analyzer requires a memory upgrade to work with the HP E2423A Preprocessor Interface. To increase the amount of memory in your HP 1650A you must install the 10449A memory upgrade. For more information contact your Hewlett-Packard Sales/Service Office.

Notice that the 10449A memory upgrade only increases the inverse assembler processing space. It does not increase the 1 k state memory depth.

#### HP 1650B, HP 1652B, HP 16510A, and HP 16510B

These logic analyzers provide 1 k of memory depth with either 80 channels of 35 MHz state analysis (25 MHz state analysis for the HP 16510A) or 80 channels of 100 MHz timing analysis.

Introduction-1

#### HP 1660A/61A/62A/63A

The HP 1660A/61A/62A/63A Logic Analyzers provide 4 k of memory depth with 136 channels (HP 1660A), 102 channels (HP 1661A), 68 channels (HP 1662A), or 34 channels (HP 1663A) of 100 MHz state analysis or 250 MHz timing analysis. These logic analyzers also support various combinations of mixed state/timing analysis.

#### **HP 16511B**

This logic analyzer combination provides 1 k of memory depth with either 160 channels of 35 MHz state analysis, or 80 channels of 35 MHz state analysis and 80 channels of 100 MHz timing analysis.

#### HP 16540A,D with one HP 16541A,D Expansion Card

This logic analyzer combination provides 4 k of memory depth (16 k with the D version) with up to 64 channels of 100 MHz state or timing analysis.

#### HP 16542A (Master Card and one expansion card)

This logic analyzer combination provides 1 M of memory depth with 32 channels of 100 MHz state or timing analysis.

#### **HP 16550A**

This logic analyzer provides 4 k of memory depth with 102 channels per card of 100 MHz state analysis or 250 MHz timing analysis. The logic analyzer will also support various combinations of mixed state/timing analysis.

Introduction-2

### How to Use This Manual

This manual is organized into three chapters and two appendices:

- Chapter 1 explains how to install and configure the HP E2423A

Preprocessor Interface to perform measurements with the

supported logic analyzers. It also contains tables listing the SCSI

command sets for the different inverse assemblers.

- Chapter 2 provides reference information on the format specification and symbols configured by the HP E2423A software. It also provides information about the inverse assemblers and status encoding.

- Chapter 3 contains additional reference information including the characteristics and signal mapping for the HP E2423A Preprocessor Interface.

- Appendix A contains an overview of the Small Computer Systems Interface (SCSI). Additional information should be obtained from the appropriate standards organization for the SCSI Standard X3T9.2/86-109 Revision 10b.

- Appendix B contains information on troubleshooting problems or difficulties which may occur with the preprocessor interface.

Introduction-3

#### **Setting Up the HP E2423A**

#### Introduction

This chapter explains how to install and configure the HP E2423A Preprocessor Interface to perform measurements with the supported logic analyzers.

## **Duplicating the Master Disk**

Before you use the HP E2423A software, make a duplicate copy of the HP E2423A master disk. Then store the master disk and use the back-up copy to configure your logic analyzer. This will help prevent the possibility of losing or destroying the original files in the event the disk wears out, is damaged, or a file is accidently deleted.

To make a duplicate copy, use the Duplicate Disk operation in the disk menu of your logic analyzer. For more information, refer to the reference manual for your logic analyzer.

#### HP 16500A Software Compatibility

The HP E2423A Preprocessor Interface requires HP 16500A system and module software version V04.01 or higher. If your software version is older than V04.01, load new HP 16500A system software with a version number of V04.01 or higher before loading the HP E2423A software.

## **Equipment Supplied**

The HP E2423A SCSI Bus Preprocessor Interface consists of the following equipment:

- The preprocessor interface hardware, which includes the preprocessor interface circuit card.

- The inverse assembler software on a 3.5-inch disk.

- This user's guide.

## **Equipment** Required

The minimum equipment required for SCSI Bus analysis consists of the following items:

- An HP 1650A (with memory upgrade), HP 1650B, HP 1652B, HP 1660A/61A/62A/63A, HP 16510A, HP 16510B, HP 16511B, HP 16540/16541A,D, HP 16542A, or HP 16550A Logic Analyzer.

- The HP E2423A Preprocessor Interface and Inverse Assembler.

- An additional cable to connect the HP E2423A to your SCSI bus system (see pages 1-4 and 1-5).

#### Installation Quick Reference

The following procedure describes the major steps required to perform measurements with the HP E2423A Preprocessor Interface. The page numbers listed in the various steps refer you to sections in this user's guide that offer more detailed information.

To prevent equipment damage, be sure to remove power from both the logic analyzer and the SCSI bus devices whenever the preprocessor interface or logic analyzer is being connected or disconnected.

- 1. Select the appropriate bus mode (Single-Ended or Differential), bus size (8-bit or 16-bit), and parity on the front panel of the HP E2423A (see page 1-3).

- 2. Connect the logic analyzer probes to the preprocessor interface board as listed in table 1-1 (see page 1-8 and 1-9).

- 3. Connect the HP E2423A SCSI Bus Preprocessor Interface to your SCSI bus system (see page 1-4).

- 4. Load the configuration file into the logic analyzer by loading the appropriate file from the flexible disk (see page 1-10).

- 5. Load the appropriate inverse assembler from the flexible disk (see page 1-11).

## Setting Up the HP E2423A Front Panel

The HP E2423A has three switches on the front panel:

**Bus Mode.** Allows the user to test either a Single-Ended or a Differential Bus system. This switch setting must match the type of SCSI bus you are currently monitoring.

Bus Size. Allows the user to select either 8-bit or 16-bit bus size.

**State Parity Check.** The use of the parity bit is not mandatory on a SCSI bus system. This switch allows the user to switch off the parity check.

Excessive parity errors may appear on screen if parity is on with a system that does not use parity.

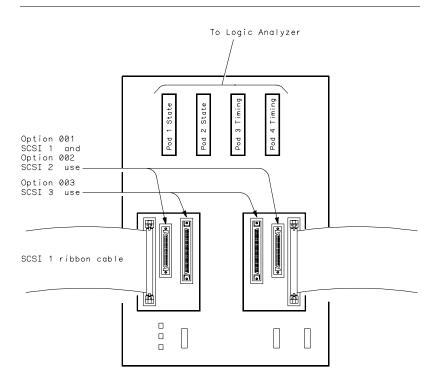

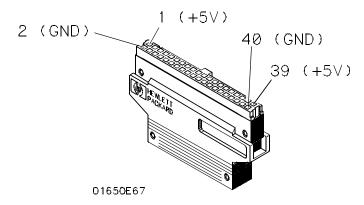

Figure 1-1. SCSI Preprocessor Interface Connectors

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

## Connecting the HP E2423A to the SCSI Bus

The connectors on the HP E2423A are tied in parallel so that all the connectors and cable combinations can be used with a Single-Ended or Differential Bus. Also, there are always four connectors that are not used. These connectors may be used for additional analysis with an oscilloscope or other measurement device.

Figure 1-1 (previous page) shows the connectors on the SCSI Preprocessor Interface. There are three types of connectors on the front panel:

- Two 68-pin D-Shell shielded high-density type;

- Two 50-pin D-Shell shielded high-density type; and

- Two 50-pin (25-pin dual row, 0.1" spacing) nonshielded connectors (see Caution on next page).

You will always need at least one additional cable to connect the HP E2423A to your SCSI bus system. The following cable/connector options are available from your HP Sales/Service Office:

| <ul> <li>E2423A Option 001</li> </ul> | 1 meter, 50-pin HD screw (m) to          |

|---------------------------------------|------------------------------------------|

|                                       | 50-pin LD bail (m). This option contains |

|                                       | two of the cables described above.       |

| <ul> <li>E2423A Option 002</li> </ul> | 1 meter, 50-pin HD screw (m) to          |

|                                       | 50-pin HD screw (m).                     |

| <ul> <li>E2423A Option 003</li> </ul> | 1 meter, 68-pin HD screw (m) to          |

|                                       | 68-pin HD screw (m).                     |

If your SCSI Bus system requires different connectors or cables than those listed above, you will have to either make or obtain adapter cables. HP Direct Marketing (1-800-538-8787) has a variety of cables with different lengths, connectors, and locking technologies. They might have a cable which meets your requirements.

The following section provides instructions for connecting the cables to the SCSI bus and the HP E2423A Preprocessor Interface.

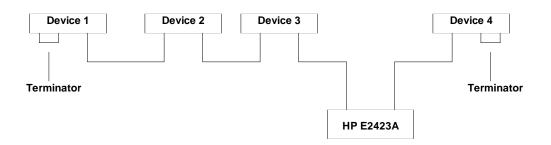

To connect the HP E2423A to the bus, daisy chain the connectors so both of the matching connectors are used together (see figure 1-2). This is accomplished by the following steps:

- 1. Turn off the power to the bus system and logic analyzer.

- 2. Disconnect one end of a cable from the bus system and connect it to one of the connectors on the HP E2423A.

- 3. Connect the optional or custom cable from the matching connector on the HP E2423A to your bus system.

- 4. Turn on the bus and logic analyzer.

You can also connect the HP E2423A to either end of your SCSI bus system. Remove the termination device from one end of the SCSI bus, and use the appropriate cable to connect the HP E2423A to the SCSI bus. Connect the termination device to the matching connector on the opposite side of the HP E2423A board.

Some 50-pin ribbon cables have a connector clamped in the center of the cable for connecting devices to the SCSI bus with only a single connection. Do not use a center connector to connect the HP E2423A to the SCSI bus. Since the circuitry of the HP E2423A is part of the transmission line for the SCSI bus, a center connector will cause stublength violations and the SCSI bus might not operate properly. You should always have a cable or termination device on both of the matching connectors on the HP E2423A.

Figure 1-2. Connecting to the SCSI Bus

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

1-5

### Connecting to the HP E2423A

Connect the logic analyzer probes to the cable connectors as listed in table 1-1. The column heads refer to the logic analyzer pods, while designations such as P1 refer to a connector on the preprocessor interface.

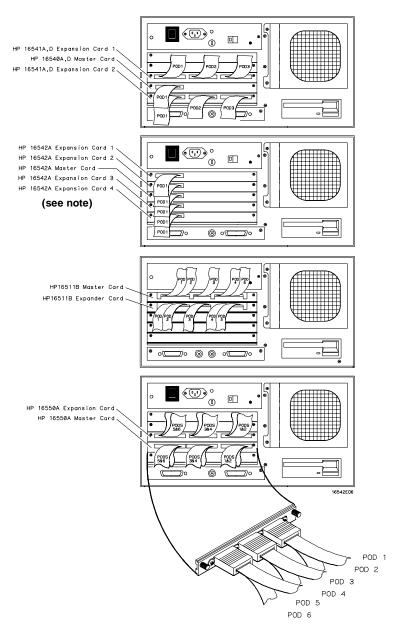

Figure 1-3 shows the relative locations of the logic analyzer cards.

#### Note

#### HP 16542A with three or four Expansion Cards

The locations for the HP 16542A expansion cards, relative to the Master Card, depend on the number of expansion cards used. If one or two expansion cards are used, Card 1 is located above the Master Card and Card 2 is located below the Master Card. If three expansion cards are used, two of them are located above the Master Card and the third is located below the Master Card. When four expansion cards are used, they are located as shown in figure 1-3.

Table 1-1 shows the physical location and connections for a one-expansion-card system.

## Power Up / Down Sequence

When powering up, the logic analyzer must be powered up first, and then the target system. The logic analyzer provides the power to the active circuits on the preprocessor interface; unpowered circuits may cause improper operation of the target system.

When powering down, the target system should be powered down first, and then the logic analyzer.

Figure 1-3. Logic Analyzer Card Locations (relative locations, actual slots used may vary)

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

1-7

Table 1-1. Logic Analyzer Connections and Configuration Files ( HP 1650 series, HP 16510A/B, HP 16511B, HP 16540/16541A,D, HP 16550A)

| Logic Analyzer                          | File                       | Pod 6 | Pod 5 | Pod 4                | Pod 3                | Pod 2                | Pod 1                        |

|-----------------------------------------|----------------------------|-------|-------|----------------------|----------------------|----------------------|------------------------------|

| HP 1650A/B,<br>HP 1652B,<br>HP 16510A/B | CSCSI2<br>state,<br>timing |       |       | P4<br>Timing<br>DATA | P3<br>Timing<br>STAT | P2<br>State<br>DATA  | P1<br>State<br>STAT<br>clk ↓ |

| HP 16511B<br>Upper Card                 | DSCSI2<br>state,<br>timing |       |       |                      |                      | P2<br>State<br>DATA  | P1<br>State<br>STAT<br>clk ↓ |

| HP 16511B<br>Lower Card                 |                            |       |       |                      |                      | P4<br>Timing<br>DATA | P3<br>Timing<br>STAT         |

| HP 16541A,D<br>Exp. Card 1              | ESCSI2ST state             |       |       |                      | P4<br>Timing<br>DATA | P3<br>Timing<br>STAT | P2<br>State<br>DATA          |

| HP 16540A,D<br>Master Card              | ESCSI2TM timing            |       |       |                      |                      |                      | P1<br>State<br>STAT<br>clk ↓ |

| HP 16550A                               | FSCSI2<br>state,<br>timing |       |       | P4<br>Timing<br>DATA | P3<br>Timing<br>STAT | P2<br>State<br>DATA  | P1<br>State<br>STAT<br>clk ↓ |

Table 1-1. Logic Analyzer Connections and Configuration Files ( HP 1660 series, HP 16542A)

| Logic Analyzer           | File                       | Pod 6 | Pod 5 | Pod 4                | Pod 3                | Pod 2               | Pod 1                        |

|--------------------------|----------------------------|-------|-------|----------------------|----------------------|---------------------|------------------------------|

| HP 16542A<br>Exp. Card 1 | ESCSI2ST state             |       |       |                      |                      |                     | P2<br>State<br>DATA          |

| HP 16542A<br>Master Card |                            |       |       |                      |                      |                     | P1<br>State<br>STAT<br>clk ↓ |

| HP 16542A<br>Exp. Card 1 | ESCSI2TM timing            |       |       |                      |                      |                     | P4<br>Timing<br>DATA         |

| HP 16542A<br>Master Card |                            |       |       |                      |                      |                     | P3<br>Timing<br>STAT         |

| HP 1660A/<br>61A/62A     | FSCSI2<br>state,<br>timing |       |       | P4<br>Timing<br>DATA | P3<br>Timing<br>STAT | P2<br>State<br>DATA | P1<br>State<br>STAT<br>clk ↓ |

| HP 1663A                 | FSCSI2 (state only)        |       |       |                      |                      | P2<br>State<br>DATA | P1<br>State<br>STAT<br>clk ↓ |

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

## Setting Up the Analyzer from the Disk

The logic analyzer is configured for SCSI bus analysis by loading the appropriate configuration file. The configuration files also load the inverse assembler "ISCSIDIR." You can then load a different inverse assembler from the list on page 1-12.

For all logic analyzers except the HP 16540/16541A,D and HP 16542A, the same configuration file is used for state or timing analysis. For the HP 16540/16541A,D and HP 16542A, separate configuration files are provided for state and timing. To load the files:

- 1. Install the HP E2423A disk in the logic analyzer front disk drive.

- 2. Select one of the following menus:

- For the HP 1650-series logic analyzers, select the I/O Disk Operations menu;

- For the HP 16500-series and HP 1660-series logic analyzers, select the System Front Disk menu.

- 3. Configure the menu to "Load" the analyzer configuration from disk.

- 4. For HP 16500-series and HP 1660-series logic analyzers, select the appropriate module (such as "100/500 MHz LA" or "Analyzer") for the load.

- 5. Use the knob to select the appropriate configuration file (see table 1-1).

- 6. Execute the load operation to load the file into the logic analyzer.

DO NOT Autoscale the timing analyzer. The Autoscale operation will destroy the previously loaded configuration. The only way to recover the configuration after Autoscale is to reload it from the disk.

## Loading an Inverse Assembler

The following section describes the different inverse assemblers available with the HP E2423A. To load a different inverse assembler after loading the configuration file:

- 1. Install the HP E2423A disk in the front disk drive of the logic analyzer.

- 2. Select one of the following menus:

- For the HP 1650-series logic analyzers, select the I/O Disk Operations menu;

- For the HP 16500-series and HP 1660-series logic analyzers, select the System Front Disk menu.

- 3. Configure the menu to "Load" the inverse assembler from disk.

- 4. For HP 16500-series and HP 1660-series logic analyzers, select the appropriate module (such as "100/500 MHz LA" or "Analyzer") for the load.

- 5. Use the knob to select the appropriate inverse assembler (see table 1-2, next page).

- 6. Execute the load operation to load the file into the logic analyzer.

To properly load the HP E2423A inverse assemblers, Analyzer 1 of the logic analyzer must be on and configured as a State machine. If Analyzer 1 and 2 are on and configured as State machines, a field will appear on screen to allow you to select which analyzer to load the inverse assembler into. Load the HP E2423A inverse assembler into Analyzer 1.

## Selecting the Correct Inverse Assembler

The HP E2423A has seven inverse assemblers available for SCSI Bus system analysis. The interpretation of the SCSI command set varies in each inverse assembler to match the applications of various device types. Only one inverse assembler can be used at a time. Table 1-2 lists the different inverse assemblers and the devices which are generally supported by the command sets.

There is a good possibility that your SCSI Bus system will be made up of several different device types, and each device type will interpret the commands differently. For example, a disk drive connected to a communication device contains two different device types. In this situation you may need to decide which inverse assembler will best fit your needs. To make it easier to select the appropriate inverse assembler, the commands for each device type are listed in tables 1-3 through 1-9. By comparing the commands for each inverse assembler, the most appropriate inverse assembler can be selected. The commands which are common to all devices are listed in normal type, and the commands which vary from device to device are listed in bold type.

A different inverse assembler can be loaded into the logic analyzer without losing the accumulated data.

Table 1-2. Inverse Assemblers

| Inverse Assembler | Devices Supported                                                     |

|-------------------|-----------------------------------------------------------------------|

| ISCSIDIR          | Direct Devices, Write Once Read Multiple Devices, and Optical Devices |

| ISCSISEQ          | Sequential Devices like tape backup drives, and Scanner Devices       |

| ISCSIPTR          | Printers                                                              |

| ISCSIPRC          | Processor Devices                                                     |

| ISCSIDSE          | A special application which is used when there is a Sequential Access |

|                   | Device on the SCSI Bus that uses Group 0 (6 byte) commands which      |

|                   | communicates with a Direct Access Device that uses Group 1 (10 byte)  |

|                   | commands                                                              |

| ISCSIAMC          | Automatic Media Changers, and Communication Devices                   |

| ISCSICDR          | CD ROMs                                                               |

Setting Up the HP E2423A 1-12

HP E2423A SCSI Bus Preprocessor Interface

Table 1-3. ISCSIDIR Commands

| 00 Test Unit Ready 24 Set Wind 25 Read Ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | dow 40 41                                                                                                                                | Change Definition                                                                                                                                             |                                                                      |                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03         Request Sense         28         Read           04         Format Unit         29         Read Ge           05         Read Block Limits         2A         Write           07         Reassign Block         2B         Seek           08         Read         2C         Erase           0A         Write         2D         Read Up           0B         Seek         Block           0F         Read Reverse         2E         Write an           10         Write Filemarks         2F         Verify           11         Space         30         Search H           12         Inquiry         31         Search H           13         Verify         32         Search L           14         Recovered Buffer         33         Set Limit           15         Mode Select         34         Pre-Fetc           16         Reserve         35         Flush Ca           17         Release         36         Lock/Un           18         Copy         Cache | deneration 43 44 45 47 48 48 49 49 49 49 48 40 40 40 41 48 40 40 40 41 45 55 5A 46 46 40 40 41 48 40 40 40 40 40 40 40 40 40 40 40 40 40 | Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense | A6<br>A8<br>A9<br>AA<br>AC<br>AE<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5 | Play Audio Exchange Medium Read Play Track Write Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element Status |

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

1-13

Table 1-4. ISCSISEQ Commands

| 13 Verify 32 Search Low 4D Log Sense B6 Send Volume Ta                                         | Gı                                                                                                                               | Group 0 Commands<br>(6 byte)                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                | Group 1 Commands<br>(10 byte)                                                                                                                                                                                                                                                            |                                                                      | Group 2 Commands<br>(10 byte)                                                                                                                                             |                                                                            | Group 5 Commands<br>(12 byte)                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1E Prevent/Allow 3C Read Buffer Removal 3D Update Block 1F Read Log 3E Read Long 3F Write Long | 01<br>03<br>04<br>05<br>07<br>08<br>0A<br>0B<br>0F<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>1A<br>1B<br>1C | Rewind Request Sense Format Unit Read Block Limits Reassign Block Read Write Seek Read Reverse Write Filemarks Space Inquiry Verify Recovered Buffer Mode Select Reserve Unit Release Unit Copy Erase Mode Sense Load/Unload Receive Diagnostics Send Diagnostics Prevent/Allow Removal | 25<br>28<br>29<br>2A<br>2B<br>2C<br>2D<br>2E<br>2F<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>3A<br>3B<br>3C<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D<br>3D | Read Generation Send Locate Erase Read Update Block Write and Verify Verify Search High Object Position Search Low Set Limits Read Position/Get Buffer Flush Cache Lock/Unlock Cache Read Defect Data Media Scan Compare Copy and Verify Write Buffer Read Buffer Update Block Read Long | 41<br>42<br>43<br>44<br>45<br>47<br>48<br>49<br>4B<br>4C<br>4D<br>55 | Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense Mode Select | A6<br>A8<br>AA<br>AC<br>AE<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5<br>B6<br>B7 | Exchange Medium Read Write Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element |  |

Setting Up the HP E2423A 1-14

HP E2423A SCSI Bus Preprocessor Interface

Table 1-5. ISCSIPTR Commands

| G                                                                                      | Group 0 Commands<br>(6 byte)                                                                                                                                                                                                                                                                          |                                                    | Group 1 Commands<br>(10 byte)                                                                                                                                                                                                   |                | Group 2 Commands<br>(10 byte)                                                                                                                                                                          |                                                                            | Group 5 Commands<br>(12 byte)                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0B<br>0F<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>1A<br>1B<br>1C | Test Unit Ready Rezero Request Sense Format Unit Read Block Limits Reassign Block Read Print Slew and Print Read Reverse Sync Buffer Space Inquiry Verify Recover Buffer Data Mode Select Reserve Release Copy Erase Mode Sense Stop Print Receive Diagnostics Send Diagnostics Prevent/Allow Removal | 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D | Set Window Read Capacity Read Read Generation Write Seek Erase Read Update Block Write and Verify Verify Search High Search = Search Low Set Limits Pre-Fetch Flush Cache Lock/Unlock Cache Read Defect Data Media Scan Compare | 4C<br>4D<br>55 | Change Definition Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense Mode Select Mode Sense | A6<br>A8<br>AA<br>AC<br>AE<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5<br>B6<br>B7 | Play Audio Exchange Medium Read Write Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element Status |  |

| 1F                                                                                     | Removal<br>Read Log                                                                                                                                                                                                                                                                                   | 3F                                                 | Write Long                                                                                                                                                                                                                      |                |                                                                                                                                                                                                        |                                                                            |                                                                                                                                                                                                        |  |

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A 1-15

Table 1-6. ISCSIPRC Commands

| Group 0 Commands                                                                                                                                                                                                                                                                                                                                                                    | Group 1 Commands                                                                                                                                                                                                                                                                                                                                                                           | Group 2 Commands                                                                                                                                                                                                                                 | Group 5 Commands                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (6 byte)                                                                                                                                                                                                                                                                                                                                                                            | (10 byte)                                                                                                                                                                                                                                                                                                                                                                                  | (10 byte)                                                                                                                                                                                                                                        | (12 byte)                                                                                                                                                                                                                                           |  |

| 00 Test Unit Ready 01 Rezero 03 Request Sense 04 Format Unit 05 Read Block Limi 07 Reassign Block 08 Receive 0A Send 0B Seek 0F Read Reverse 10 Write Filemarks 11 Space 12 Inquiry 13 Verify 14 Recovered Buffer 15 Mode Select 16 Reserve 17 Release 18 Copy 19 Erase 1A Mode Sense 1B Start/Stop 1C Receive Diagnostics 1D Send Diagnostics 1E Prevent/Allow Removal 1F Read Log | 24 Set Window 25 Read Capacity 28 Read 29 Read Generation 8 2A Write 2B Seek 2C Erase 2D Read Update Block 2E Write and Verify 2F Verify 30 Search High 31 Search = 32 Search Low 33 Set Limits 34 Pre-Fetch 35 Flush Cache 36 Lock/Unlock Cache 37 Read Defect Data 38 Media Scan 39 Compare 3A Copy and Verify 3B Write Buffer 3C Read Buffer 3D Update Block 3E Read Long 3F Write Long | 40 Change Definition 41 Write Same 42 Read Sub-Channel 43 Read TOC 44 Read Header 45 Play Audio 47 Play Audio MSF 48 Play Audio Track Index 49 Play Audio Track Relative 4B Pause/Resume 4C Log Select 4D Log Sense 55 Mode Select 5A Mode Sense | A5 Play Audio A6 Exchange Medium A8 Read AA Write AC Erase AE Write and Verify AF Verify B0 Search High B1 Search Equal B2 Search Low B3 Set Limits B5 Request Volume Element Address B6 Send Volume Tag B7 Read Defect Data B8 Read Element Status |  |

Setting Up the HP E2423A 1-16

HP E2423A SCSI Bus Preprocessor Interface

Table 1-7. ISCSIDSE Commands

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Set Window                                                                                                                                                                                                           |                |                                                                                                                                                                                                        |                                                                | (12 byte)                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A         Write         2D           0B         Seek           0F         Read Reverse         2E           10         Write Filemarks         2F           11         Space         30           12         Inquiry         31           13         Verify         32           14         Recovered Buffer         33           15         Mode Select         34           16         Reserve Unit         35           17         Release Unit         36           18         Copy         37           1A         Mode Sense         38           1B         Load/Unload         39           1C         Receive         3A           Diagnostics         3B           1D         Send Diagnostics         3C           1E         Prevent/Allow         3D | Read Capacity Read Read Generation Write Seek Erase Read Update Block Write and Verify Verify Search High Search = Search Low Set Limits Pre-Fetch Flush Cache Lock/Unlock Cache Read Defect Data Media Scan Compare | 4C<br>4D<br>55 | Change Definition Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense Mode Select Mode Sense | A6<br>A8<br>A9<br>AA<br>AC<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5 | Play Audio Exchange Medium Read Play Track Write Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element Status |

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A 1-17

Table 1-8. ISCSIAMC Commands

| Group 0 Commands (6 byte)  Group 1 Commands (10 byte)                                  |                                                                                                                                                                                                                                                                                                                  | G                                               | roup 2 Commands<br>(10 byte)                                                                                                                                                                                                                                                                                                                | Group 5 Commands<br>(12 byte) |                                                                                                                                                                                                        |                                                                            |                                                                                                                                                                                                                       |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0B<br>0F<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>1A<br>1B<br>1C | Test Unit Ready Rezero Request Sense Format Unit Read Block Limits Initialize Element Status Read Write Seek Read Reverse Write Filemarks Space Inquiry Verify Recovered Buffer Mode Select Reserve Release Copy Erase Mode Sense Start/Stop Receive Diagnostics Send Diagnostics Prevent/Allow Removal Read Log | 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D | Set Window Read Capacity Get Message Read Generation Send Message Position to Element Erase Read Update Block Write and Verify Verify Search High Search Equal Search Low Set Limits Pre-Fetch Flush Cache Lock/Unlock Cache Read Defect Data Media Scan Compare Copy and Verify Write Buffer Read Buffer Update Block Read Long Write Long | 4C<br>4D<br>55                | Change Definition Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense Mode Select Mode Sense | A6<br>A8<br>AA<br>AC<br>AE<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5<br>B6<br>B7 | Move Medium Exchange Medium Get Message Send Message Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element Status |  |

Setting Up the HP E2423A 1-18

HP E2423A SCSI Bus Preprocessor Interface

Table 1-9. ISCSICDR Commands

| Gro                                                                                                                                                                           | up 0 Commands<br>(6 byte)                                                                                                                                                                                                                                                                            | Gı                                                 | roup 1 Commands<br>(10 byte)                                                                                                                                                  | G              | roup 2 Commands<br>(10 byte)                                                                                                                                                                           | Group 5 Commands<br>(12 byte)                                              |                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 01 R<br>03 R<br>04 F<br>05 R<br>07 R<br>08 R<br>0A V<br>0B S<br>0F R<br>10 V<br>11 S<br>12 II<br>13 V<br>14 R<br>15 M<br>16 R<br>17 R<br>18 C<br>19 E<br>1A M<br>1B S<br>1C R | Test Unit Ready Rezero Request Sense Format Unit Read Block Limits Reassign Block Read Write Seek Read Reverse Write Filemarks Space nquiry Verify Recovered Buffer Mode Select Reserve Release Copy Erase Mode Sense Start/Stop Receive Diagnostics Send Diagnostics Prevent/Allow Removal Read Log | 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D | Seek X Erase Read Update Block Write and Verify Verify Search High Search = Search Low Set Limits Pre-Fetch Flush Cache Lock/Unlock Cache Read Defect Data Media Scan Compare | 4C<br>4D<br>55 | Change Definition Write Same Read Sub-Channel Read TOC Read Header Play Audio Play Audio MSF Play Audio Track Index Play Audio Track Relative Pause/Resume Log Select Log Sense Mode Select Mode Sense | A6<br>A8<br>AA<br>AC<br>AE<br>AF<br>B0<br>B1<br>B2<br>B3<br>B5<br>B6<br>B7 | Play Audio Exchange Medium Read Write Erase Write and Verify Verify Search High Search Equal Search Low Set Limits Request Volume Element Address Send Volume Tag Read Defect Data Read Element Status |  |  |  |

HP E2423A SCSI Bus Preprocessor Interface Setting Up the HP E2423A

1-19

#### **Analyzing the SCSI Bus**

#### Introduction

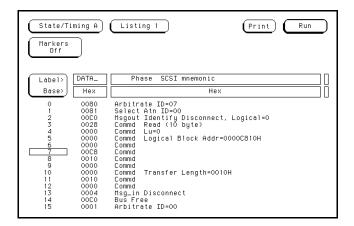

This chapter provides reference information on the format specification and symbols configured by the HP E2423A software. It also provides information about the inverse assemblers and LED indicators.

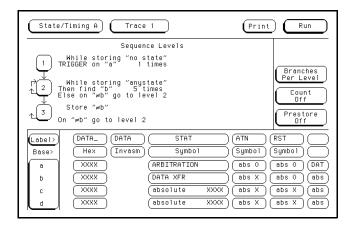

## Format Specification

The HP E2423A software sets up format specifications for the logic analyzer. There will be some slight differences in the displays, according to which logic analyzer you are using. For example, some of the logic analyzers do not have a Clock Period field.

The ADDR, DATA\_, and DATA labels all contain the same information. The ADDR field is required by the inverse assembler software, but the information is not applicable for SCSI bus analysis. The DATA\_ field shows the data in hexadecimal format in the Listing menu. The DATA field is decoded and shows the instruction in SCSI mnemonics.

Chapter 3 lists the SCSI bus signals for the HP E2423A and their corresponding lines to the logic analyzer.

#### Note

For those logic analyzers which have a Clock Period field (HP 1650A, HP 1650B, HP 1652B, HP 16510A, HP 16510B, and HP 16511B), the Clock Period field should remain in the current selection (> 60 ns) since the SCSI bus has bus cycle periods greater than 60 ns. For more information on the Clock Period field, refer to the reference manual for your logic analyzer.

## Symbols and Labels

The configuration file sets up symbol tables on the logic analyzer. The tables contain alphanumeric values which identify data patterns.

Table 2-1 lists the bits assigned to the STAT and BUSIZE labels. Table 2-2 lists the symbols for the STAT label. Table 2-3 lists the symbols for the PHASE label.

Table 2-1. STAT Label and BUSIZE Label Bits

| Bit | Signal | Description                                                                                                     |

|-----|--------|-----------------------------------------------------------------------------------------------------------------|

| 0   | I/O    | This signal is true when data flows to the initiator and false when data flows to the target.                   |

| 1   | C/D    | This signal is true when not in the data phase and false when in the data phase.                                |

| 2   | MSG    | This signal is true when in the message phase and false when not in the message phase.                          |

| 3   | SEL    | This signal is true during selection of target device.                                                          |

| 4   | BSY    | This signal is true when the bus is in use and false when the bus is free or during selection of target device. |

| 5   | REQ    | This signal is a handshake driven by the target device.                                                         |

| 6   | ACK    | This signal is a handshake driven by the initiator.                                                             |

| 7   | ATN    | This signal is used by the initiator to request an output phase.                                                |

| 8   | RST    | A true signal resets all devices on the bus.                                                                    |

Table 2-1. STAT Label and BUSIZE Label Bits (continued)

| Bit                     | Signal | Description                                                                      |

|-------------------------|--------|----------------------------------------------------------------------------------|

| 9                       | LBUSPT | DBP Low byte bus parity bit (odd).                                               |

| 10                      | HBUSPT | DBP1 High byte bus parity bit (odd).                                             |

| 11                      | LPTYER | DBP Error. This bit is true when there is a low byte parity error.               |

| 12                      | HPTYER | DBP1 Error. This bit is true when there is a high byte parity error.             |

| 15<br>(BUSIZE<br>Label) | BUSIZE | This bit sends the position of the Bus Size switch on the HP E2423A front panel. |

Table 2-2. STAT Symbols

| Symbol                                                                                          |   |   |   |   |                                     | Pa                                      | tterr | 1 |   |   |   |   |   |

|-------------------------------------------------------------------------------------------------|---|---|---|---|-------------------------------------|-----------------------------------------|-------|---|---|---|---|---|---|

| RST BUS FREE                                                                                    | X | X | X | X | 1                                   | X                                       | X     | X | 0 | 0 | X | X | X |

| RESET                                                                                           | X | X | X | X | 1                                   | X                                       | X     | X | X | X | X | X | X |

| BUS FREE                                                                                        | X | X | X | X | 0                                   | X                                       | X     | X | 0 | 0 | X | X | X |

| ARBITRATION                                                                                     | X | X | X | X | 0                                   | 0                                       | 0     | 0 | 1 | 1 | 0 | 0 | 0 |

| ATTEN ARBIT                                                                                     | X | X | X | X | 0                                   | 1                                       | 0     | 0 | 1 | 1 | X | X | X |

| HL_PTY ERROR                                                                                    | 1 | 1 | X | X | 0                                   | X                                       | X     | X | X | X | X | X | X |

| L_PTY ERROR                                                                                     | 0 | 1 | X | X | 0                                   | X                                       | X     | X | X | X | X | X | X |

| H_PTY ERROR                                                                                     | 1 | 0 | X | X | 0                                   | X                                       | X     | X | X | X | X | X | X |